# (11) **EP 2 834 840 B1**

(12)

# **EUROPEAN PATENT SPECIFICATION**

(45) Date of publication and mention of the grant of the patent:28.12.2016 Bulletin 2016/52

(21) Application number: 13794179.5

(22) Date of filing: 16.05.2013

(51) Int Cl.: H01L 21/677 (2006.01) B B65G 49/07 (2006.01)

B81C 1/00 (2006.01)

(86) International application number: PCT/US2013/041441

(87) International publication number: WO 2013/176963 (28.11.2013 Gazette 2013/48)

#### (54) MICRO DEVICE TRANSFER HEAD WITH SILICON ELECTRODE

MIKROVORRICHTUNGS-ÜBERTRAGUNGSKOPF MIT EINER SILICIUMELEKTRODE TÊTE DE TRANSFERT DE MICRODISPOSITIF À ÉLECTRODE EN SILICIUM

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

- (30) Priority: **25.05.2012 US 201213481592**

- (43) Date of publication of application: 11.02.2015 Bulletin 2015/07

- (60) Divisional application: **16188068.7**

- (73) Proprietor: Apple Inc.

Cupertino, CA 95014-2084 (US)

(72) Inventors:

- GOLDA, Dariusz Santa Clara California 95054 (US)

- BIBL, Andreas

Los Altos, California 94024 (US)

- (74) Representative: Barnfather, Karl Jon Withers & Rogers LLP

4 More London Riverside London SE1 2AU (GB)

- (56) References cited:

WO-A1-2011/072372 JP-A- 2004 079 745 KR-A- 20020 022 557 KR-A- 20040 030 610 KR-A- 20110 075 451 US-A1- 2005 232 728 US-A1- 2011 121 462

P 2 834 840 B1

Note: Within nine months of the publication of the mention of the grant of the European patent in the European Patent Bulletin, any person may give notice to the European Patent Office of opposition to that patent, in accordance with the Implementing Regulations. Notice of opposition shall not be deemed to have been filed until the opposition fee has been paid. (Art. 99(1) European Patent Convention).

40

## **BACKGROUND**

#### **FIELD**

**[0001]** The present invention relates to micro devices. More particularly embodiments of the present invention relate to a micro device transfer head and a method of transferring one or more micro devices to a receiving substrate.

#### **BACKGROUND INFORMATION**

**[0002]** Integration and packaging issues are one of the main obstacles for the commercialization of micro devices such as radio frequency (RF) microelectromechanical systems (MEMS) microswitches, light-emitting diode (LED) display systems, and MEMS or quartz-based oscillators.

[0003] Traditional technologies for transferring of devices include transfer by wafer bonding from a transfer wafer to a receiving wafer. One such implementation is "direct printing" involving one bonding step of an array of devices from a transfer wafer to a receiving wafer, followed by removal of the transfer wafer. Another such implementation is "transfer printing" involving two bonding/de-bonding steps. In transfer printing a transfer wafer may pick up an array of devices from a donor wafer, and then bond the array of devices to a receiving wafer, followed by removal of the transfer wafer.

**[0004]** Some printing process variations have been developed where a device can be selectively bonded and de-bonded during the transfer process. In both traditional and variations of the direct printing and transfer printing technologies, the transfer wafer is de-bonded from a device after bonding the device to the receiving wafer. In addition, the entire transfer wafer with the array of devices is involved in the transfer process.

**[0005]** Document WO 2011/072372 discloses a method and electrostatic transfer stamp for transferring semiconductor dice using electrostatic transfer printing techniques.

# **SUMMARY OF THE INVENTION**

**[0006]** A micro device transfer head and head array, and a method of transferring one or more micro devices to a receiving substrate are disclosed. For example, the receiving substrate may be, but is not limited to, a display substrate, a lighting substrate, a substrate with functional devices such as transistors or integrated circuits (ICs), or a substrate with metal redistribution lines.

[0007] In an embodiment, a micro device transfer head array includes a base substrate and a patterned silicon layer over the base substrate. The patterned silicon layer includes a silicon interconnect and an array of silicon electrodes electrically connected with the silicon inter-

connect. Each silicon electrode includes a mesa structure that protrudes above the silicon interconnect. A dielectric layer such as silicon oxide, hafnium oxide, aluminum oxide, or tantalum oxide, covers a top surface of each mesa structure. Each silicon electrode may optionally include an electrode lead.

**[0008]** The patterned silicon layer may be the top silicon layer in a silicon-on-insulator (SOI) substrate including the top silicon layer, a buried oxide layer, and base silicon substrate. In an embodiment, the base silicon substrate is a (100) bulk silicon substrate. The top silicon layer may be doped, for example, with a n-dopant such as phosphorus.

[0009] In an embodiment a via extends through the base substrate from a backside of the base substrate to the patterned silicon layer, and the via is in electrical connection with the silicon interconnect and the array of silicon electrodes. In an embodiment, the via extends through the buried oxide layer between the patterned silicon layer and the base substrate. The via may have straight or tapered sidewalls. A passivation layer may cover a side surface of the via within the base substrate. The via may terminate at a bottom surface of the patterned silicon layer or extend through the patterned silicon layer. Where the via terminates at a bottom surface of the patterned silicon layer a conductive layer may be formed on the passivation layer in the via, and in electrical contact with the bottom surface of the patterned silicon layer. Where the via extends through the patterned silicon layer, a conductive layer may be formed on the passivation layer in the via, and in electrical contact with an interior side surface of the patterned silicon layer. The conductive layer may also partially cover a top surface of the patterned silicon layer. The portion of the conductive layer partially covering a top surface of the patterned silicon layer may have a different thickness than the portion of the conductive layer on the passivation layer. Whether the via terminates at a bottom surface of the patterned silicon layer or extends through the patterned silicon layer, the conductive layer may not completely fill the via. In an embodiment, the dielectric layer is partially formed within the via.

[0010] In an embodiment, the micro device transfer head array includes a base silicon substrate, a patterned silicon layer over the base silicon substrate, and a buried silicon oxide layer between the patterned silicon layer and the base silicon substrate. The patterned silicon layer includes a silicon interconnect and an array of silicon electrodes electrically connected with the silicon interconnect. Each silicon electrode includes a mesa structure that protrudes above the silicon interconnect. A via extends through the base silicon substrate and the buried silicon oxide layer from a backside of the base silicon substrate to the patterned silicon layer, and in electrical connection with the silicon interconnect and the array of silicon electrodes. As silicon oxide passivation layer covers a side surface of the via within the base silicon substrate. The via may terminate at a bottom surface of the

patterned silicon layer or extend through the patterned silicon layer. A dielectric layer such as silicon oxide, hafnium oxide, aluminum oxide, or tantalum oxide, covers a top surface of each mesa structure.

[0011] In an embodiment, the micro device transfer head array includes first and second vias extending through the base substrate from the backside of the base substrate to the patterned silicon layer. The first via is in electrical connection with a first silicon interconnect and a first array of silicon electrodes, and the second via is in electrical connection with a second silicon interconnect and a second array of silicon electrodes. The first and second arrays of silicon electrodes may be aligned to form an array of bipolar silicon electrodes. The first and second vias may terminate at a bottom surface of the patterned silicon layer or extend through the patterned silicon layer. In an embodiment, a first dielectric layer is located on the patterned silicon layer, and is removed from over the mesa structures, and the dielectric layer covering the top surface of each mesa structure has a higher dielectric constant or dielectric breakdown strength than the first dielectric layer.

[0012] In an embodiment, a method of forming a micro device transfer head array includes etching a top silicon layer of a SOI stack to form a silicon interconnect and a plurality of silicon electrodes electrically connected with the silicon interconnect, with each silicon electrode including a mesa structure that protrudes above the silicon interconnect. A dielectric layer is then formed over the plurality of silicon electrodes through deposition, or thermal oxidation of the patterned silicon layer. Etching the top silicon layer may include first forming a mask layer on the top silicon layer, and patterning the mask layer to form a plurality of islands. The mask layer can be formed by deposition, or thermal oxidation of the top silicon layer. The plurality of islands can then be used as an etching mask to etch a plurality of trenches partially through the top silicon layer. The plurality of islands are then removed and a blanket etching can be performed on the top silicon layer to complete formation of the silicon interconnect and the plurality of silicon electrodes, with etching stopping on the buried oxide layer.

**[0013]** In an embodiment, a portion of the dielectric layer is removed from over the plurality of mesa structures, and a second dielectric layer is deposited over the plurality of mesa structure. In an embodiment, the second dielectric layer has a higher dielectric constant or breakdown voltage than the dielectric layer. The second dielectric layer can be deposited using a technique such as atomic layer deposition.

[0014] In an embodiment, a mask layer is formed on an SOI stack that includes the top silicon layer over a buried oxide layer, a base substrate under the buried oxide layer, and a bottom passivation layer under the base substrate. A via opening is etched through the bottom passivation layer, the base substrate, and the buried oxide layer, and a patterned conductive layer is then formed within the via opening to make electrical contact

with the silicon interconnect and the plurality of silicon electrodes. For example, the patterned conductive layer can be formed by depositing through a shadow mask.

[0015] The via opening through the bas substrate may have straight sidewalls when formed using dry reactive ion etching (DRIE) or tapered sidewalls when formed using potassium hydroxide (KOH) solution. Etching of the via opening may include forming a smaller opening within the buried oxide layer than in the base substrate. Side surfaces of the via opening within the base substrate can be thermally oxidized to form a passivation layer covering the side surface of the via opening prior to forming the patterned conductive layer within the opening. For example, thermally oxidizing the side surfaces of the via opening can be performed simultaneously with thermally oxidizing the plurality of silicon electrodes to form the dielectric layer over the plurality of silicon electrodes.

[0016] In an embodiment, a mask layer is formed on an SOI stack that includes the top silicon layer over a buried oxide layer, a base substrate under the buried oxide layer, and a bottom passivation layer under the base substrate. A backside via opening is etched through the bottom passivation layer and the base substrate stopping on the buried oxide layer. A topside via opening is etched through the dielectric layer, the silicon layer, and the buried oxide layer so that the topside via opening connects with the backside via opening. A patterned conductive layer can then be deposited within the topside via opening over an exposed top surface of the silicon interconnect and within an interior side surface of the silicon interconnect. A second patterned conductive layer can then be deposited within the backside via opening and in electrical contact with the patterned conductive layer. Deposition of the patterned conductive layers can be accomplished with deposition through shadow masks.

## **BRIEF DESCRIPTION OF THE DRAWINGS**

### [0017]

40

45

50

55

FIG. 1A is a plan view illustration of a bipolar micro device transfer head in accordance with an embodiment of the invention.

FIG. 1B includes a combination plan view and combination cross-section side view illustration taken along lines V-V, W-W, X-X, Y-Y, and Z-Z from FIG. 1A in accordance with an embodiment of the invention.

FIG. 2A is a combination cross-sectional side view illustration taken along lines V-V, W-W, X-X, Y-Y, and Z-Z from FIG. 1A in accordance with an embodiment of the invention.

FIG. 2B is a combination plan view illustration taken along lines V-V, W-W, X-X, Y-Y, and Z-Z from FIG. 1A in accordance with an embodiment of the invention

FIG. 3A is a combination cross-sectional side view illustration of a bipolar micro device transfer head

30

40

45

50

including topside and backside via openings in accordance with an embodiment of the invention.

FIG. 3B is a combination top plan view of a bipolar micro device transfer head including topside and backside via openings in accordance with an embodiment of the invention.

FIG. 4A is a combination cross-sectional side view illustration of a bipolar micro device transfer head including tapered backside via openings in accordance with an embodiment of the invention.

FIG. 4B is a combination top plan view of a bipolar micro device transfer head including tapered backside via openings in accordance with an embodiment of the invention.

FIG. 5A is a combination cross-sectional side view illustration of a bipolar micro device transfer head including deposited dielectric layer in accordance with an embodiment of the invention.

FIG. 5B is a combination top plan view of a bipolar micro device transfer head including deposited dielectric layer in accordance with an embodiment of the invention.

FIGS. 6A-14B illustrate a method of forming a bipolar micro device transfer head including backside via openings in accordance with an embodiment of the invention.

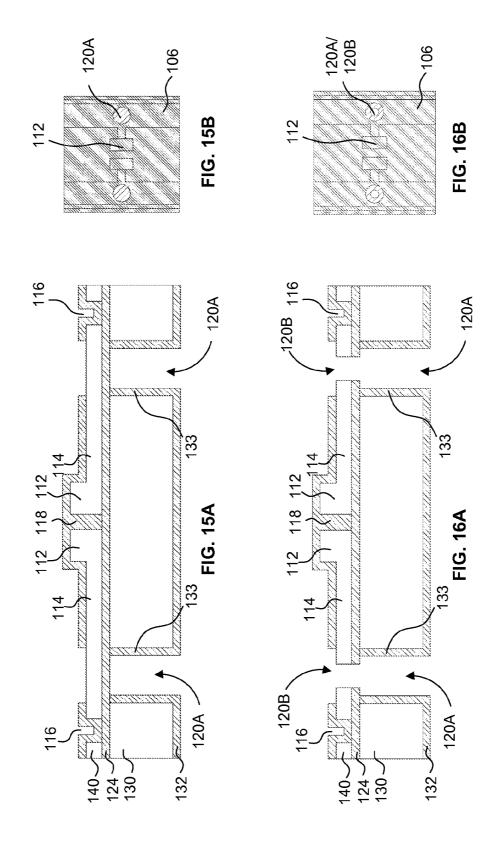

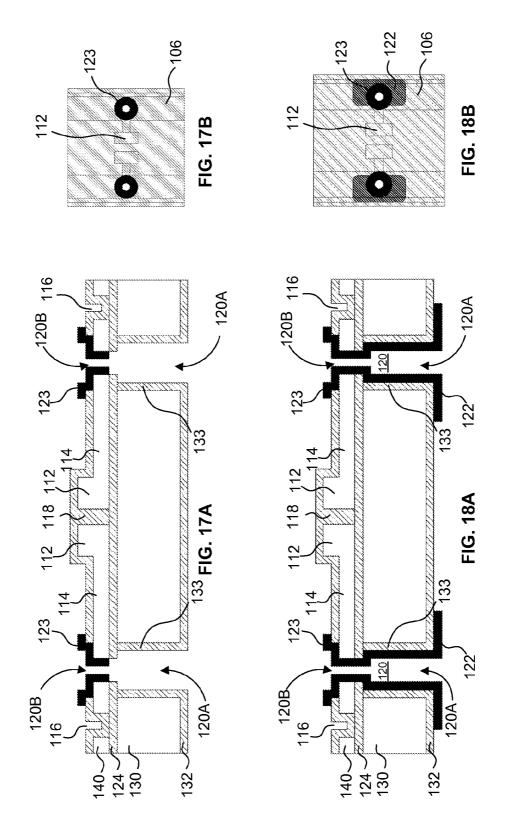

FIGS. 15A-18B illustrate a method of forming a bipolar micro device transfer head including topside and backside via openings in accordance with an embodiment of the invention.

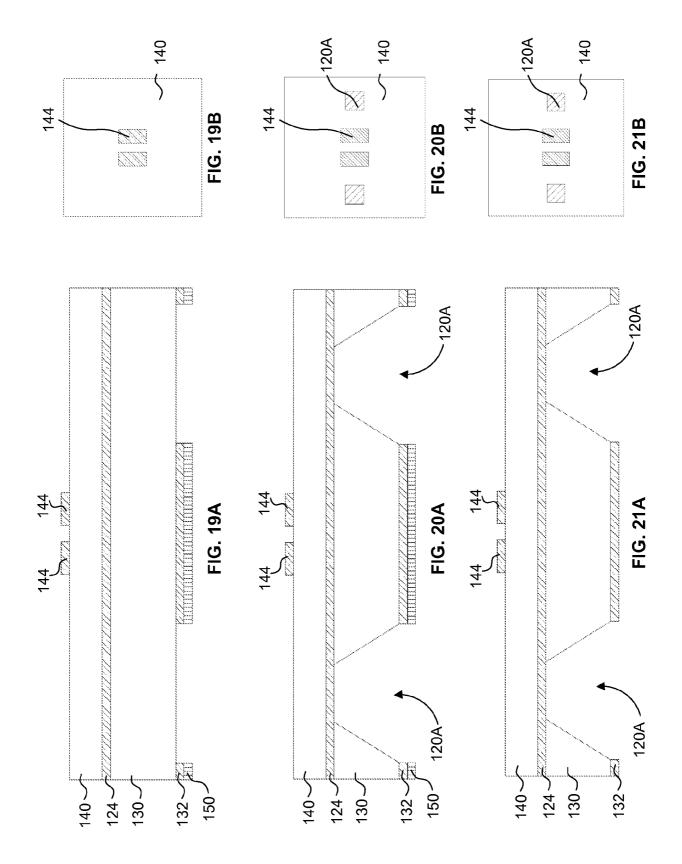

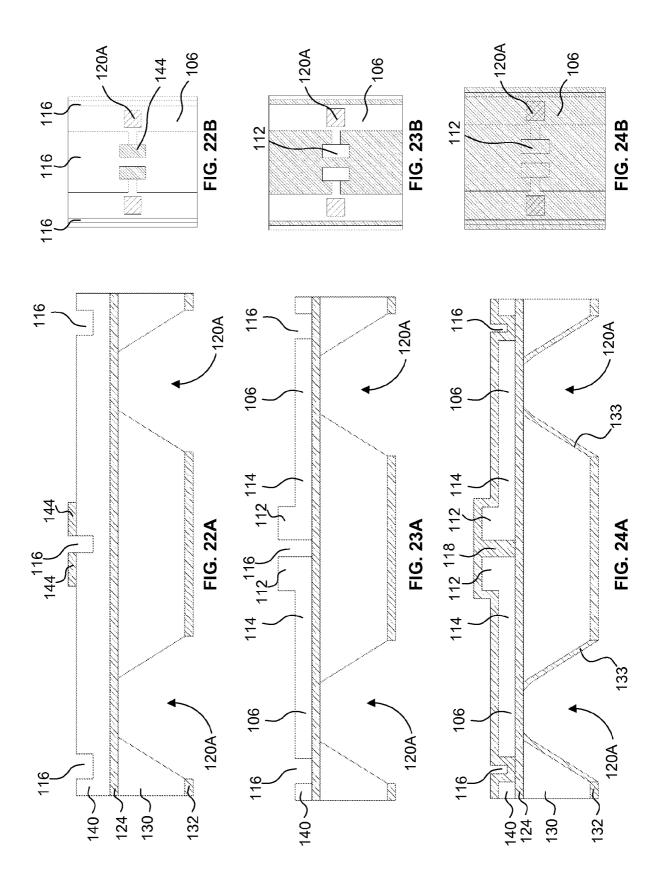

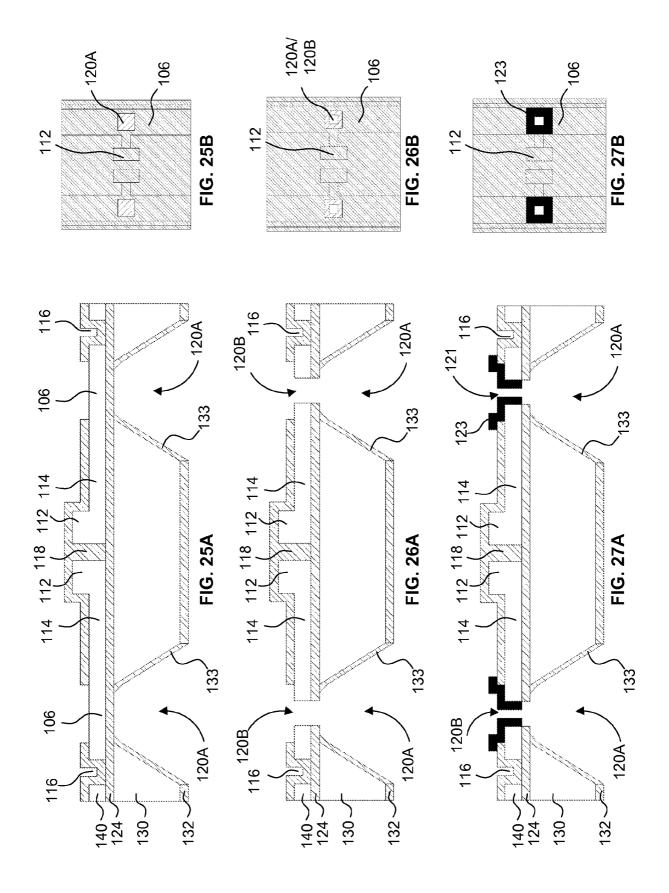

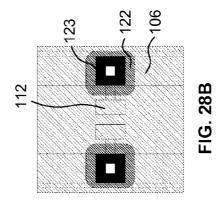

FIGS. 19A-28B illustrate a method of forming a bipolar micro device transfer head including backside via openings with tapered sidewalls in accordance with an embodiment of the invention.

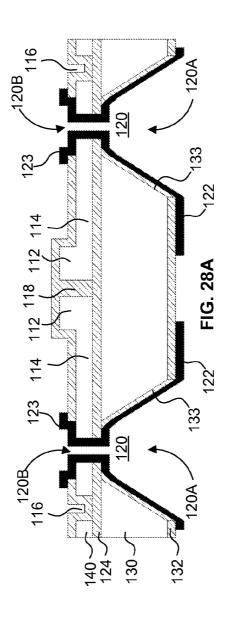

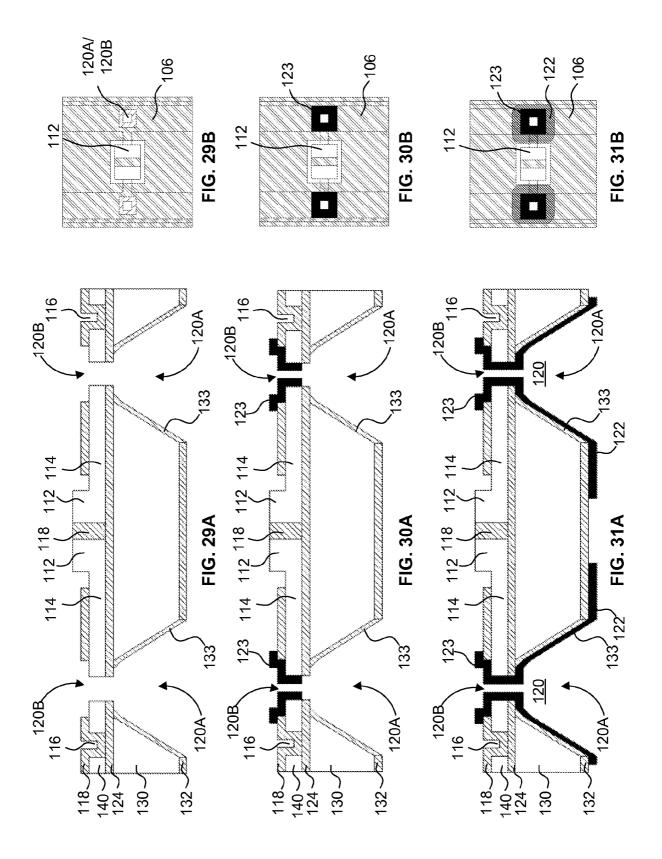

FIGS. 29A-32B illustrate a method of forming a bipolar micro device transfer head including a replacement electrode dielectric in accordance with an embodiment of the invention.

FIG. 33 is a flow chart illustrating a method of picking up and transferring an array of micro devices from a carrier substrate to a receiving substrate in accordance with an embodiment of the invention.

FIG. 34 is a cross-sectional side view illustration of an array of micro device transfer heads positioned over an array of micro devices on a carrier substrate in accordance with an embodiment of the invention. FIG. 35 is a cross-sectional side view illustration of an array of micro device transfer heads in contact with an array of micro devices in accordance with an embodiment of the invention.

FIG. 36 is a cross-sectional side view illustration of an array of transfer heads picking up an array of micro devices in accordance with an embodiment of the invention.

FIG. 37 is a cross-sectional side view illustration of an array of micro devices released onto a receiving substrate in accordance with an embodiment of the invention.

#### **DETAILED DESCRIPTION OF THE INVENTION**

[0018] Embodiments of the present invention describe a micro device transfer head and head array, and method of transferring a micro device and an array of micro devices to a receiving substrate. For example, the micro device transfer head and head array may be used to transfer micro devices such as, but not limited to, diodes, LEDs, transistors, ICs, and MEMS from a carrier substrate to a receiving substrate such as, but not limited to, a display substrate, a lighting substrate, a substrate with functional devices such as transistors or integrated circuits (ICs), or a substrate with metal redistribution lines. [0019] In various embodiments, description is made with reference to figures. However, certain embodiments may be practiced without one or more of these specific details, or in combination with other known methods and configurations. In the following description, numerous specific details are set forth, such as specific configurations, dimensions and processes, etc., in order to provide a thorough understanding of the present invention. In other instances, well-known semiconductor processes and manufacturing techniques have not been described in particular detail in order to not unnecessarily obscure the present invention. Reference throughout this specification to "one embodiment," "an embodiment" or the like means that a particular feature, structure, configuration, or characteristic described in connection with the embodiment is included in at least one embodiment of the invention. Thus, the appearances of the phrase "in one embodiment," "an embodiment" or the like in various places throughout this specification are not necessarily referring to the same embodiment of the invention. Furthermore, the particular features, structures, configurations, or characteristics may be combined in any suitable manner in one or more embodiments.

**[0020]** The terms "over", "to", "between" and "on" as used herein may refer to a relative position of one layer with respect to other layers. One layer "over" or "on" another layer or bonded "to" another layer may be directly in contact with the other layer or may have one or more intervening layers. One layer "between" layers may be directly in contact with the layers or may have one or more intervening layers.

[0021] The terms "micro" device or "micro" LED structure as used herein may refer to the descriptive size of certain devices or structures in accordance with embodiments of the invention. As used herein, the terms "micro" devices or structures are meant to refer to the scale of 1 to 100 μm. However, it is to be appreciated that embodiments of the present invention are not necessarily so limited, and that certain aspects of the embodiments may be applicable to larger, and possibly smaller size scales. [0022] In one aspect, without being limited to a particular theory, embodiments of the invention describe micro device transfer heads and head arrays which operate in accordance with principles of electrostatic grippers, using the attraction of opposite charges to pick up micro

35

40

45

50

devices. In accordance with embodiments of the present invention, a pull-in voltage is applied to a micro device transfer head in order to generate a grip pressure on a micro device and pick up the micro device.

[0023] In another aspect, embodiments of the invention describe a manner of forming an array of micro device transfer heads from a commercially available siliconon-insulator (SOI) substrate including a base substrate, buried oxide layer, and a top silicon device layer. In such an embodiment, a silicon interconnect and an array of electrodes are formed from the top silicon layer of the SOI substrate. Each individual transfer head includes one or more silicon electrodes. For example, the transfer heads may include monopolor or bipolar electrodes. In an embodiment, a bipolar electrostatic transfer head includes a pair of silicon electrodes, where each silicon electrode includes a mesa structure and optionally an electrode lead. The mesa structures for the pair of silicon electrodes protrude above their respective silicon interconnects to provide a localized contact point to pick up a specific micro device during a pick up operation. In this manner, it is not necessary to form patterned metal electrodes. It has been observed that when patterning of metal electrodes and electrode leads using a negative photoresist, for example, it can be difficult to control exposure of the photoresist at different depths (e.g. along both a top surface and down sidewalls of a mesa structure). Peeling of the patterned metal layers has also been observed during photoresist removal, potentially affecting operability of the transfer heads. In accordance with embodiments of the present invention, it is not required to form a patterned metal electrode over a mesa structure. Instead, the protruding profile of the mesa structure is formed by patterning the silicon electrode to include a raised portion corresponding to the mesa structure which protrudes away from the base substrate and above the silicon interconnect.

[0024] Silicon electrodes prepared in accordance with embodiments of the invention may include integrally formed mesa structures which are substantially taller compared to non-integrally formed mesa structures with patterned metal electrodes. Photolithography can limit patterned metal electrode structures to heights of 5 -10 μm, whereas silicon electrode mesa structures can be up to 20-30  $\mu m$  or taller. The mesa structure height for a silicon electrode structure is limited by the etch aspect ratio and the electrode gap (e.g. between a pair of bipolar silicon electrodes). In an embodiment, aspect ratios for silicon electrode mesa structures can range from 10-20:1. For example, silicon electrode mesa structures in a bipolar electrode configuration can be 20 µm tall separated by a 2 µm gap between the mesa structures. Taller electrode structures may also afford larger clearance for contaminant particles and reduce the effects of stray filed on un-targeted micro devices. When compared to metalized mesa structures, silicon electrodes with integrally formed mesa structures can be more robust to surface contamination and errors in planar alignment of

the micro device transfer head in relation to the micro device carrier substrate.

[0025] In another aspect, embodiments of the invention describe a manner of forming an array of micro device transfer heads from a commercially available siliconon-insulator (SOI) substrate which allows for a processing sequence with minimal processing steps. The processing sequence does not require metal deposition and patterning steps to form metal electrodes, which relieves thermal processing constraints and allows for the formation of dielectric and passivation layers by high temperature thermal oxidation resulting in reduced deposition and patterning operations.

[0026] In another aspect, embodiments of the invention describe a transfer head and transfer head array including vias extending through the base substrate from a backside of the base substrate to the patterned silicon layer for connecting the electrodes with working circuitry of a transfer head assembly. The processing sequence in accordance with embodiments of the invention also enables passivation of the vias extending through the base substrate with high temperature thermal oxide growth.

[0027] In yet another aspect, embodiments of the invention describe a manner for mass transfer of an array of pre-fabricated micro devices with an array of transfer heads. For example, the pre-fabricated micro devices may have a specific functionality such as, but not limited to, a LED for light-emission, silicon IC for logic and memory, and gallium arsenide (GaAs) circuits for radio frequency (RF) communications. In some embodiments, arrays of micro LED devices which are poised for pick up are described as having a 10  $\mu$ m by 10  $\mu$ m pitch, or 5  $\mu$ m by 5  $\mu$ m pitch. At these densities a 6 inch substrate, for example, can accommodate approximately 165 million micro LED devices with a 10  $\mu$ m by 10  $\mu$ m pitch, or approximately 660 million micro LED devices with a 5 μm by 5 μm pitch. A transfer tool including an array of transfer heads matching an integer multiple of the pitch of the corresponding array of micro LED devices can be used to pick up and transfer the array of micro LED devices to a receiving substrate. In this manner, it is possible to integrate and assemble micro LED devices into heterogeneously integrated systems, including substrates of any size ranging from micro displays to large area displays, and at high transfer rates. For example, a 1 cm by 1 cm array of micro device transfer heads can pick up and transfer more than 100,000 micro devices, with larger arrays of micro device transfer heads being capable of transferring more micro devices. Each transfer head in the array of transfer heads may also be independently controllable, which enables selective pick up and release of the micro devices.

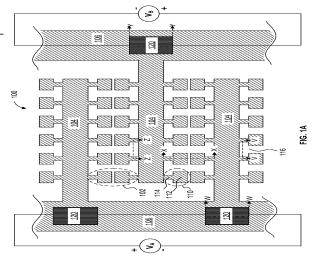

**[0028]** Referring now to FIG. 1A, a plan view illustration is provided for a portion of a micro device transfer head array and includes views at different depths. In the particular embodiment illustrated, the hatch shading illustrates an arrangement of silicon electrodes and silicon

interconnects as viewed from the top surface of the micro device transfer head array, and the darker shading illustrates a backside via connection as viewed from the backside surface of the micro device transfer head array. In this manner, the plan view illustration provides detail regarding structures which have been formed from both sides of the SOI wafer.

[0029] As illustrated, the micro device transfer head array 100 includes an array of transfer heads 102 connected by an arrangement of silicon trace interconnects 104, and silicon bus interconnects 106. As illustrated, silicon bus interconnects 106 may be formed around a periphery or outside a working area of the transfer head array including the array of transfer heads 102. In an embodiment, each transfer head 102 includes a pair of silicon electrodes 110, with each silicon electrode 110 including a mesa structure 112 and optionally an electrode lead 114 connected to a silicon interconnect 104. [0030] In an embodiment, a plurality of vias 120 are formed through the backside of the base substrate to the patterned silicon layer to make contact with silicon interconnects 106 in order to electrically connect the silicon electrodes 110 with working circuitry of a transfer head assembly. In the embodiment illustrated in FIG. 1A, the silicon bus interconnect 106 on the left side of the illustration may be connected to a first voltage source V<sub>A</sub>, and the silicon interconnect 106 on the right side of the illustration may be connected to a second voltage source V<sub>B</sub>. Where each transfer head 102 is operable as a bipolar transfer head, voltage sources V<sub>A</sub> and V<sub>B</sub> may simultaneously apply opposite voltages so that each of the silicon electrodes 110 in a respective transfer head 102 has an opposite voltage.

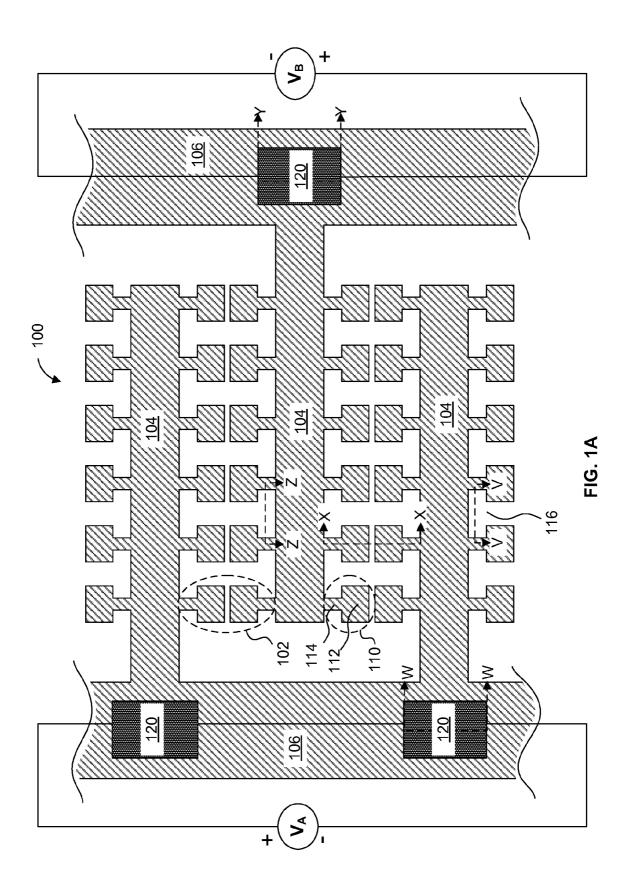

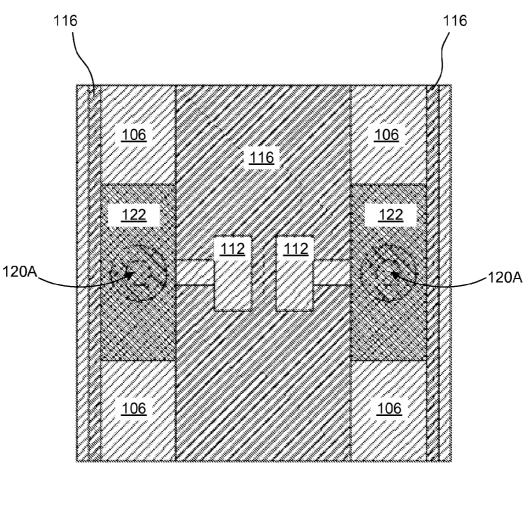

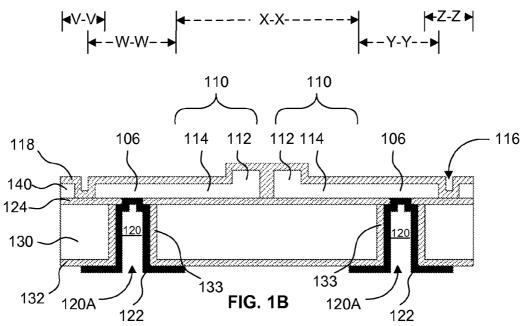

[0031] Referring now to FIG. 1B, a combination plan view illustration and combination cross-sectional side view illustration are provided taken along lines V-V, W-W, X-X, Y-Y, and Z-Z from FIG. 1A. The combination views are not representations of the precise relative locations for all of the different features illustrated, rather the combination views combine specific features at different locations in FIG. 1A in a single illustration to more easily represent the processing sequence. For example, while the cross-sectional side view illustration shows one via 120 corresponding to one silicon electrode 110, it is clear from FIG. 1A that one via 120 may be electrically connected with a plurality of silicon electrodes 110 along one or more silicon interconnects 104. As illustrated, lines V-V and Z-Z are along one or more trenches 116 between adjacent silicon electrodes 110. Referring again to FIG. 1A, one or more trenches 116 may be formed around all silicon electrodes 110, and between silicon interconnects 104, 106. As illustrated, lines W-W and Y-Y are along backside vias 120. As illustrated, line X-X is across a bipolar transfer head including a pair of silicon electrodes

[0032] Still referring to FIG. 1B, a silicon electrode 110 includes a mesa structure 112 and optionally an electrode lead 114, where the mesa structure 112 is an ele-

vated portion of the silicon electrode 110. A dielectric layer 118 may cover a top surface of the pair of silicon electrodes 110. Dielectric layer 118 may also cover a side surface of the mesa structures 112 laterally between the pair of mesa structure 112 for the pair of silicon electrodes 110 in a bipolar transfer head 102. A via opening 120A extends through the base substrate 130 from a backside of the base substrate to the patterned silicon layer 140 where silicon interconnect 106 is located. In the particular embodiment illustrated in FIG. 1B, the via opening 120A extends through a buried oxide layer 124 and terminates at a bottom surface of the patterned silicon layer 140 where silicon interconnect 106 is located. A passivation layer 132 is formed on the backside of the base substrate 130, and a passivation layer 133 is formed on side surfaces within the via opening 120A. Where base substrate is formed of silicon, the passivation layers 132, 133 insulate electrical shorting between the vias 120. The buried oxide layer 124 also insulates electrical shorting between the silicon electrodes 110, and silicon interconnects 104, 106.

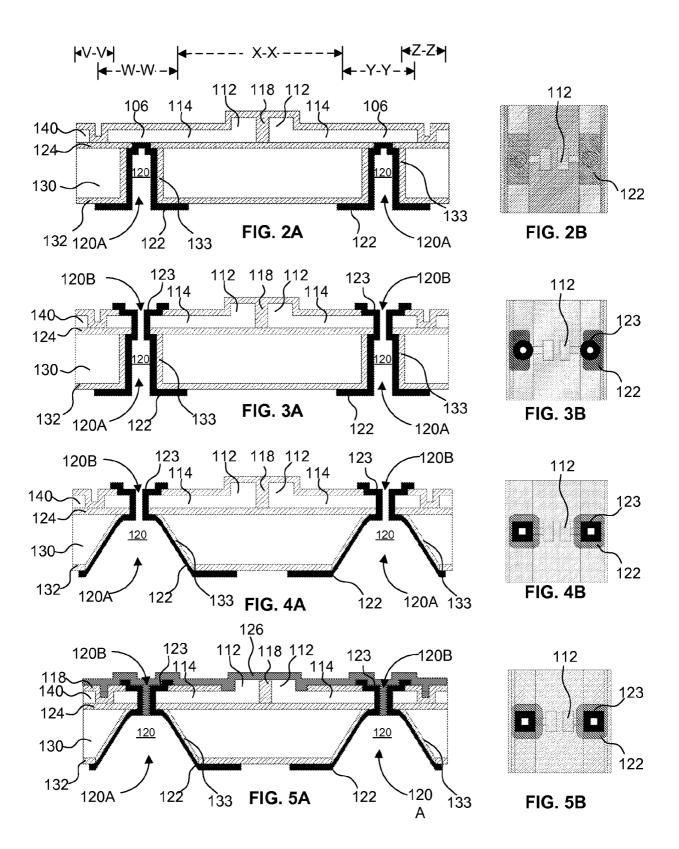

**[0033]** Referring now to FIGS. 2A-2B, FIGS. 3A-3B, FIGS. 4A-4B, and FIGS. 5A-5B, various different transfer head array configurations in accordance with embodiments of the invention are illustrated side-by-side. It is to be understood that while the following variations are separately illustrated and described, the variations are not necessarily incompatible with one another, and that the variations may be combined in any suitable manner in one or more embodiment.

[0034] FIGS. 2A-2B are the combination plan view illustration and combination cross-sectional side view illustration described above with regard to FIG. 1B. FIGS. 3A-3B, FIGS. 4A-4B, and FIGS. 5A-5B are combination plan view illustrations and combination cross-sectional side view illustrations prepared similarly as those in FIG. 1B. Therefore, the combination views are not representations of the precise relative locations for all of the different features illustrated, rather combination views combine specific features at different locations previously identified in FIG. 1A in order to more easily represent the particular variations in processing sequences.

[0035] As previously described with regard to FIG. 1B, the vias 120 illustrated in FIG. 2A-2B extend through the base substrate 130 from a backside of the base substrate to a patterned silicon layer 140. In an embodiment, vias 120 contact one or more silicon bus interconnects 106 in the patterned silicon layer 140. In other embodiments, vias 120 may contact other features or silicon interconnects in the patterned silicon layer 140. Via 120 along line W-W may be electrically connected to a first silicon interconnect 106 which is connected to a first voltage source V<sub>A</sub>, and via 120 along line Y-Y may be electrically connected to a second silicon interconnect 106 which is connected to a second voltage source V<sub>B</sub>. In the particular embodiment illustrated, via openings 120A extend through a buried oxide layer 124 and terminate at a bottom surface of a silicon interconnect 106. A passivation

40

45

50

55

25

40

layer 132 is formed on the backside of the base substrate 130 and on side surfaces within the via openings 120A. A conductive layer 122 is formed on the passivation layer 133 and is in electrical contact with the bottom surface of a silicon interconnect 106. In the particular embodiment illustrated, the conductive layers 122 do not completely fill the via openings 120A, and the conductive layers 122 are physically and electrically separated in order to prevent shorting between vias 120 connected to different voltage sources  $V_A$ ,  $V_B$ . In an embodiment, vias 120 which are electrically connected to the same voltage source may or may not be physically and electrically connected. For example, a conductive layer 122 may span across both vias 120 on the left side of FIG. 1A, and also be electrically and physically separated from the via 120 taken along line Y-Y on the right side of FIG. 1A.

[0036] Referring now to FIGS. 3A-3B, in one embodiment topside via opening 120B may be formed over the backside via opening 120B to form via 120. As will become more apparent in the following description, the topside via opening 120B may be formed in order make electrical contact with the silicon interconnects 106 and to form an opening through the buried oxide layer 124 without the lithographic challenges associated with not adversely affecting the passivation layer 133 along the sidewalls of via openings 120A. A conductive layer 123 can optionally be formed over the exposed top surface of the silicon interconnects 106 and within an interior side surface of the silicon interconnects 106. In this manner, partially forming conductive layer 123 over the top surface of the silicon interconnect 106 can provide greater surface area for ohmic contact with the silicon interconnects 106. Due to the closer proximity of the silicon interconnect 106 to the top surface of the SOI structure than the backside surface of the SOI structure, in accordance with some embodiments, it may be more efficient to form a layer of conductive layer 123 within the interior side surface of silicon interconnect 106 from above the top surface of the SOI structure as opposed to from the back surface of the SOI structure. Conductive layer 123 may be formed from the same or different material from conductive layer 122. Conductive layers 122, 123 may form a continuous conductive layer along the via 120 side surfaces.

[0037] Referring now to FIGS. 4A-4B, in one embodiment the backside via opening 120A includes tapered sidewalls in order to more efficiently form passivation layer 133 along sidewalls of the via opening 120A, and conductive layer 122 on the passivation layer 133 and on interior side surfaces of silicon interconnect 106. It is to be appreciated, that while FIGS. 4A-4B are illustrated as a variation of FIGS. 3A-3B, that the feature of tapered sidewalls in backside via opening 120A can be combined with the embodiment illustrated in FIGS. 2A-2B, and that a topside via opening 120B is not required for the formation of tapered sidewalls in backside via opening 120A. For example, the tapered sidewalls may partially alleviate the lithographic challenges associated with forming

openings in the buried oxide layer 124 from the backside via openings 120A while not adversely affecting the passivation layer 133 along the sidewalls of via openings 120A.

[0038] Referring now to FIGS. 5A-5B, in one embodiment, dielectric layer 118 may be partially or completely removed. In the particular embodiment illustrated in FIGS. 5A-5B, the dielectric layer 118 is removed from over the mesa structures 112. A second dielectric layer 126 is formed over the top surface of mesa structures 112 and over the remaining topography of the transfer head array, which may include portions of dielectric layer 118. Dielectric layer 126 may also cover the topside via openings 120B and corresponding conductive layers 123, and may partially or completely fill the topside via openings 120B within the silicon interconnects 106. In an embodiment, dielectric layer 126 has a higher dielectric constant and/or dielectric breakdown strength than dielectric layer 118. In an embodiment, dielectric layer 118 is thermally grown SiO<sub>2</sub>, and dielectric layer 126 is atomic layer deposition (ALD) SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub>, or RuO<sub>2</sub>. It is to be appreciated, that while FIGS. 5A-5B are illustrated as a variation of FIGS. 4A-4B, that the feature of a dielectric layer 126 can be combined with the embodiments illustrated in FIGS. 2A-2B and FIGS. 3A-3B, and that a topside via opening 120B or tapered sidewalls in backside via opening 120A are not required for the formation of dielectric layer 126.

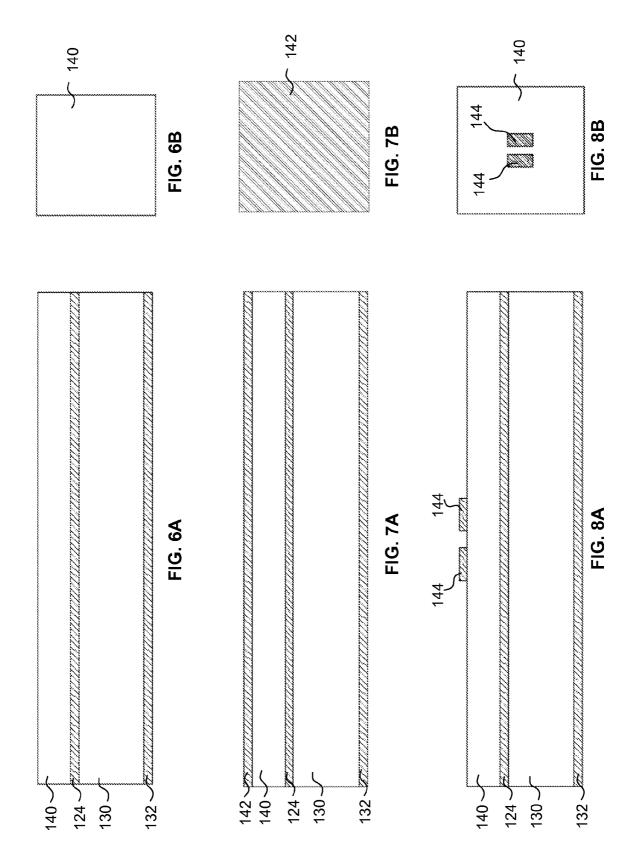

[0039] FIGS. 6A-14B illustrate a method of forming a bipolar micro device transfer head including backside via openings in accordance with an embodiment of the invention. Initially, the processing sequence may begin with a commercially available SOI substrate as illustrated in FIGS. 6A-6B. The SOI substrate may include base substrate 130, top silicon device layer 140, a buried oxide layer 124 between the base substrate and the top silicon device layer, and backside passivation layer 132. In an embodiment, base substrate is a (100) silicon handle wafer having a thickness of 500 μm +/- 50 μm, buried oxide layer 124 is 1  $\mu m$  +/- 0.1  $\mu m$  thick, and top silicon device layer is 7-20  $\mu$ m +/- 0.5  $\mu$ m thick. The top silicon device layer may also be doped to improve conductivity. For example, a phosphorous dopant concentration of approximately 10<sup>17</sup> cm<sup>-3</sup> yields a resistivity of less than 0.1 ohm-centimeter. In an embodiment, the backside passivation layer 132 is a thermal oxide having a thickness up to approximately 2 µm thick, which is the approximate upper limit for thermal oxidation of silicon.

[0040] A mask layer 142 may then be formed over the silicon device layer 140, as illustrated in FIGS. 7A-7B. Mask layer 142 may be deposited, or alternatively thermally grown from the silicon device layer 140. In an embodiment, mask layer 142 is a thermally growth  ${\rm SiO}_2$  layer having a thickness of approximately 0.1  $\mu$ m. In an embodiment, where mask layer 142 is thermally growth  ${\rm SiO}_2$ , the mask layer 142 has a thickness which is significantly less than the thickness of buried oxide ( ${\rm SiO}_2$ ) layer 124 in order to maintain structural stability for the

15

25

30

40

45

partially patterned SOI structure during removal of the patterned mask layer.

[0041] Referring to FIGS. 8A-8B, the mask layer 142 is then patterned to form an array of islands 144 which will correspond to the mesa structures of the silicon electrodes. In an embodiment, mask layer is a thermally grown SiO<sub>2</sub> layer, and islands 144 are formed by applying a positive photoresist, exposing, and removing undeveloped areas of the photoresist with a potassium hydroxide (KOH) developer solution. The mask layer 142 is then dry etched to form islands 144 using a suitable technique such as ion milling, plasma etching, reactive ion etching (RIE), or reactive ion beam etching (RIBE), electron cyclotron resonance (ECR), or inductively coupled plasma (ICP), stopping on the silicon layer 140. If a high degree of anisotropic etching is not required, a dry plasma etching technique with a plasma etchant such as CF<sub>4</sub>, SF<sub>6</sub> or NF3 may be used. The patterned photoresist is then removed by O2 ashing followed by piranha etch resulting in the structure illustrated in FIGS. 8A-8B.

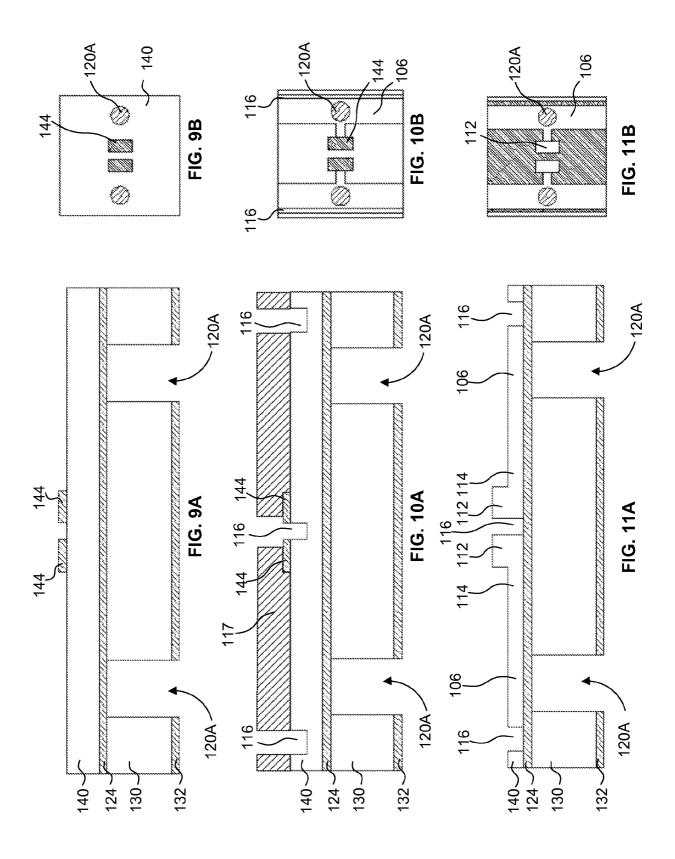

[0042] In an embodiment, backside via openings 120A are then formed in the SOI substrate. Initially, as illustrated in FIGS. 9A-9B, the backside via openings are formed through the backside passivation layer 132 and base substrate 130, stopping on the buried oxide layer 124. In an embodiment, the backside via openings 120A illustrated in FIGS. 9A-9B are formed by applying a patterned positive photoresist on the backside passivation layer 132, followed by etching of the exposed passivation layer 133 and dry reactive ion etching (DRIE) of the base substrate 130, stopping on the buried oxide layer 124. The base substrate 130 may alternatively be etched with a wet etchant such as KOH. However, KOH wet etchant attacks silicon preferentially in the (100) plane, and may produce an anisotropic V-etch. DRIE etching may be selected for more vertical sidewalls in the backside via openings 120A. After etching of the base substrate 130, the patterned positive photoresist can be removed by O<sub>2</sub> ashing followed by piranha etch resulting in the structure illustrated in FIGS. 9A-9B.

[0043] Referring to FIGS. 10A-11B, the silicon electrodes 110 and silicon interconnects 104, 106 are patterned in a two part etching sequence. First, as illustrated in FIGS. 10A-10B the top silicon layer 140 is partially etched through, defining the patterns of the silicon electrodes and silicon interconnects 104, 106. In an embodiment, this may be accomplished with a thin patterned positive photoresist, DRIE etching approximately 5 µm of a 7-10  $\mu$ m thick top silicon layer 140 in a timed etch. In accordance with embodiments of the invention, openings in the photoresist 117 (illustrated in FIG. 10A only) correspond to the size of the trenches 116 on the edges of FIG. 10A used to define the silicon electrodes 110 and silicon interconnects 104, 106, however, the openings over the islands 144 corresponding to the gap between silicon electrode mesa structures 112 may be larger than the gap between the islands 144. In this manner, the islands 144 in the patterned hard mask layer 142 can be

used to form silicon electrode mesa structures 112 with higher gap resolution between mesa structures when compared to using photoresist alone. The patterned positive photoresist can be removed using O2 ashing followed by piranha etch. Second, as illustrated in FIGS. 11A-11B with islands 144 still present, DRIE etching is continued using islands 144 as a mask to form the silicon electrodes 110 including the protruding mesa structures 112, and silicon interconnects 104, 106, stopping on the underlying buried oxide layer 124. Upon completion of etching the silicon layer 140, a dry etching technique is performed to remove the islands 144, approximately 0.1  $\mu$ m. In an embodiment, where only 0.1  $\mu$ m of oxide is removed, and the buried oxide 124 is approximately 1.0 μm thick, a significant portion of the exposed buried oxide 124 is not removed. In accordance with embodiments of the invention, the buried oxide 124 provides structural stability for the partially patterned SOI structure and a significant portion of the buried oxide 124 is not removed during removal of the islands 144. As illustrated in FIG. 11B, the buried oxide layer 124 is exposed in trenches 116 around the silicon electrodes and between the inter-

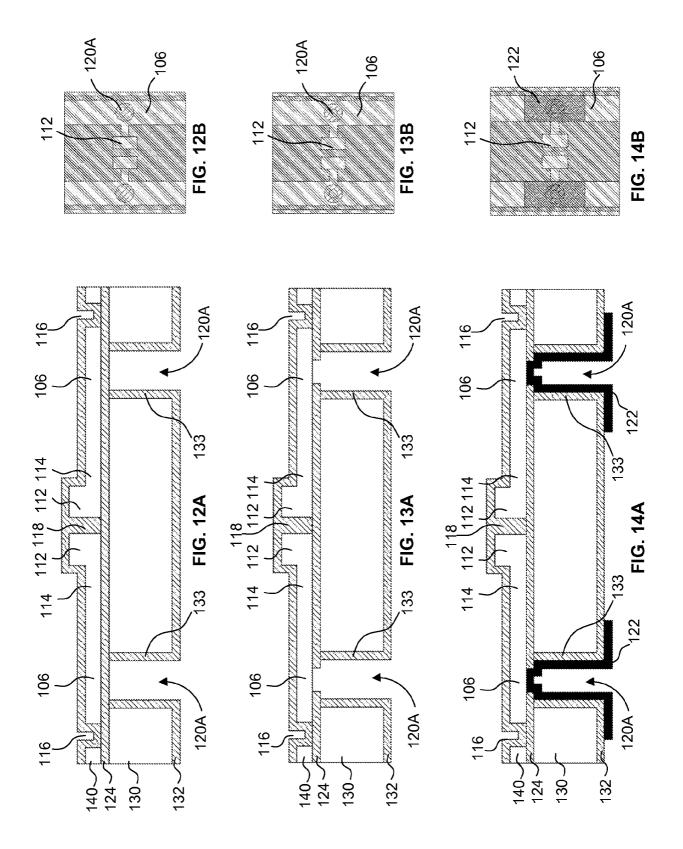

[0044] Referring now to FIGS. 12A-12B, the front and back sides of the SOI wafer can then be oxidized in order to passivate the silicon electrodes, silicon interconnects, and backside via opening. In an embodiment, high temperature wet oxidation may be performed in order to grow an approximately 1  $\mu m$  thick oxide layer 118 on the silicon electrodes 110, between the mesa structures 112, on the silicon interconnects 104, 106, and within trenches 116. An approximately 1  $\mu m$  thick oxide layer 133 is also simultaneously grown within the backside via openings 120A along sidewalls of the base substrate 130.

[0045] A dry oxide etch using a suitable dry etching technique is then performed to create openings in the buried oxide layer 124 within the backside via openings 120A to expose a bottom surface of the patterned silicon layer 140 where silicon interconnects 106 are formed, as illustrated in FIGS. 13A-13B. In an embodiment, a thin positive photoresist is formed over the backside of the SOI wafer and within the backside via opening 120A and patterned. The buried oxide layer 124 is then etched to expose a bottom surface of the silicon layer 140. As illustrated, the openings in the buried oxide layer 124 are smaller (e.g. smaller diameter or cross-section) than the openings within the base substrate 130 (including the oxide layer 133). In this manner, having a smaller opening within the buried oxide layer 124 than in the base substrate (including oxide layer 133) protects against inadvertently etching through the oxide layer 133, or undercutting the oxide layer 133 and electrically shorting the backside via 120 with the base substrate 130. Due to lithographic tolerances and resolution capabilities, the openings within the buried oxide layer 124 may have a minimum cross-section of greater than 10  $\mu$ m.

[0046] Referring now to FIGS. 14A-14B, a patterned conductive layer 122 is formed on the passivation layer

20

40

50

133 within the via openings 120A and in electrical contact with the bottom surface of the silicon interconnect 106. In an embodiment, the patterned conductive layer 122 is formed by sputtering through a shadow mask. In an embodiment, the patterned conductive layer 122 includes a first layer of 500 angstrom thick titanium (Ti), a middle layer of 500 angstrom thick titanium-tungsten (TiW), and a 1  $\mu$ m to 2  $\mu$ m thick outer layer of gold (Au). In an embodiment, the patterned conductive layer 122 makes ohmic contact with the silicon interconnects 106. Following the formation of patterned conductive layer 122, the SOI substrate may then be diced, for example using laser dicing, to form a plurality of transfer heads each including an array of transfer heads 102, interconnected with silicon interconnects 104, 106 and vias 120 extending through the base substrate 130 from a backside of the base substrate to the patterned silicon layer 140 to electrically connect the silicon electrodes 110 with working circuitry of a transfer head assembly.

[0047] FIGS. 15A-18B illustrate a method of forming a bipolar micro device transfer head including topside and backside via openings in accordance with an embodiment of the invention. The processing sequence leading up to FIGS. 15A-15B may be identical to the processing sequence of FIGS. 6A-12B. In an embodiment illustrated in FIGS. 15A-15B, openings are formed in the top dielectric layer 118 directly above the backside via openings 120A. Openings may be formed in top dielectric layer 118 with a thick patterned positive photoresist, followed by dry etching of the top dielectric layer 118. The patterned photoresist is then removed by  $\rm O_2$  ashing followed by piranha etch resulting in the structure in FIGS. 15A-15B.

[0048] Referring now to FIGS. 16A-16B, openings are formed in the silicon layer 140 and buried oxide layer 124 to form a topside via opening 120B which connects with backside via opening 120A. Openings may be formed in the silicon layer 140 and buried oxide layer 124 by forming a thick patterned positive photoresist, followed by DRIE of the silicon layer 140 stopping on the buried oxide layer 124, followed by RIE through the buried oxide layer 124. The patterned photoresist is then removed by O<sub>2</sub> ashing followed by piranha etch resulting in the structure in FIGS. 16A-16B. In this manner, forming the openings through the buried oxide layer 124 when forming the topside via openings 120B may avoid the lithographic challenges associated with forming an opening in the buried oxide layer 124 from the backside of the SOI structure without adversely affecting the passivation layer 133 along the sidewalls of the via openings 120A.

[0049] A patterned conductive layer 123 may then be formed over the exposed top surface of the silicon interconnects 106 and within an interior side surface of the silicon interconnects 106, as illustrated in FIGS. 17A-17B. In this manner, partially forming conductive layer 123 over the top surface of the silicon interconnect 106 can provide greater surface area for ohmic contact with the silicon interconnects 106. Due to the closer proximity

of the silicon interconnect 106 to the top surface of the SOI structure than the backside surface of the SOI structure, in accordance with some embodiments, it may be more efficient to form a layer of conductive layer 123 within the interior side surface of silicon interconnect 106 from above the top surface of the SOI structure as opposed to from the back surface of the SOI structure. In an embodiment, the patterned conductive layer 123 is formed by sputtering through a shadow mask. In an embodiment, the patterned conductive layer 123 includes a first layer of 500 angstrom thick titanium (Ti), a middle layer of 500 angstrom thick titanium-tungsten (TiW), and a 1  $\mu m$  to 2  $\mu m$  thick outer layer of gold (Au). In an embodiment, the patterned conductive layer 123 makes ohmic contact with the silicon interconnects 106.

[0050] Referring now to FIGS. 18A-18B, a patterned conductive layer 122 may be formed on the passivation layer 133 within the via openings 120A and in electrical contact with the patterned conductive layer 123. Conductive layer 122 may be formed from the same or different material from conductive layer 123, and may have the same or different thicknesses. In an embodiment, conductive layer 123 has a thicker layer of gold. Following the formation of patterned conductive layers 122, 123, the SOI substrate may then be diced, for example using laser dicing, to form a plurality of transfer heads each including an array of transfer heads 102, interconnected with silicon interconnects 104, 106 and vias 120 extending through the base substrate 130 from a backside of the base substrate to the patterned silicon layer 140, and through the patterned silicon layer 140, to electrically connect the silicon electrodes 110 with working circuitry of a transfer head assembly.

[0051] FIGS. 19A-28B illustrate a method of forming a bipolar micro device transfer head including backside via openings with tapered sidewalls in accordance with an embodiment of the invention. The processing sequence leading up to FIGS. 19A-19B may be identical to the processing sequence of FIGS. 6A-8B. In an embodiment illustrated in FIGS. 19A-19B, a patterned hardmask layer 150 is formed over the backside passivation layer 132 for pattering of the backside passivation layer. Hardmask layer 150 may be deposited with any suitable method such as chemical vapor deposition (CVD) or plasma enhanced chemical vapor deposition (PECVD). In an embodiment, a 2 µm thick PECVD silicon nitride hardmask layer 150 is deposited, followed by deposition of a thick patterned positive photoresist. The hardmask layer 150 and backside passivation layer 132 are then etched using RIE to form openings stopping on the base substrate 130. The patterned photoresist is then removed by O<sub>2</sub> ashing followed by piranha etch and short HF dip resulting in the structure in FIGS. 19A-19B.

[0052] Referring now to FIGS. 20A-20B, backside via openings 120A are then etched into the base substrate 130. In an embodiment, single-sided wet etching is performed using a suitable etching solution such as KOH to form backside via openings 120A with tapered sidewalls

25

40

45

in the base substrate 130 and stopping on the buried oxide layer 124. As illustrated, the via openings 120A at the bottom surface of the base substrate 130 are wider or have a larger cross-section than at a top surface of the base substrate 130 at the interface with the buried oxide layer 124. Where the base substrate 130 is (100) silicon, the KOH wet etchant may attack the silicon preferentially in the (100) plane to produce the illustrated Vetch structure. The patterned hard mask layer 150 may then be removed using a blanket nitride etching solution, as illustrated in FIGS. 21A-21B.

[0053] The following process sequence of FIGS. 22A-24B may be identical to that described above with regard to FIGS. 10A-12B, and the following process sequence of FIGS. 25A-28B may be identical to that described above with regard to FIGS. 15A-18B. It is to be appreciated that while the processing sequence for forming the final structure illustrated in FIGS. 28A-28B includes tapered sidewalls in backside via opening 120A as well as a topside via opening 120B, that a topside via opening 120B is not required for the formation of tapered sidewalls in backside via opening 120A.

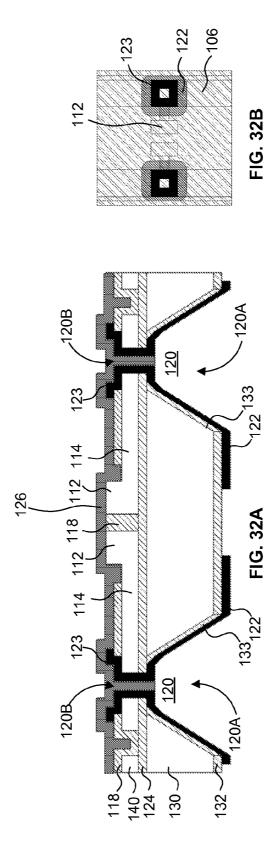

[0054] FIGS. 29A-32B illustrate a method of forming a bipolar micro device transfer head including a replacement electrode dielectric in accordance with an embodiment of the invention. The processing sequence leading up to FIGS. 29A-29B may be identical to the processing sequence of FIGS. 6A-8B and FIGS. 19A-24B. Referring now to FIGS. 29A-29B, in an embodiment openings are formed in the top dielectric layer 118 directly above the backside via openings 120A and directly over the mesa structures 112. In the particular embodiment illustrated, the dielectric layer 118 is not completely removed from between the adjacent mesa structures 112 in a bipolar electrode transfer head 102. Openings may be formed in top dielectric layer 118 with a thick patterned positive photoresist, followed by dry etching of the top dielectric layer 118. The patterned photoresist is then removed by O<sub>2</sub> ashing followed by piranha etch. Openings are then formed in the silicon layer 140 and buried oxide layer 124 to form a topside via opening 120B which connects with backside via opening 120A. Openings may be formed in the silicon layer 140 and buried oxide layer 124 by forming a thick patterned positive photoresist, followed by DRIE of the silicon layer 140 stopping on the buried oxide layer 124, followed by RIE through the buried oxide layer 124. The patterned photoresist is then removed by O2 ashing followed by piranha etch resulting in the structure in FIGS. 29A-29B.

**[0055]** A patterned conductive layer 123 is then formed over the exposed top surface of the silicon interconnects 106 and within an interior side surface of the silicon interconnects 106, as illustrated in FIGS. 30A-30B. In this manner, partially forming conductive layer 123 over the top surface of the silicon interconnect 106 can provide greater surface area for ohmic contact with the silicon interconnects 106. Due to the closer proximity of the silicon interconnect 106 to the top surface of the SOI struc-

ture than the backside surface of the SOI structure, in accordance with some embodiments, it may be more efficient to form a layer of conductive layer 123 within the interior side surface of silicon interconnect 106 from above the top surface of the SOI structure as opposed to from the back surface of the SOI structure. In an embodiment, the patterned conductive layer 123 is formed by sputtering through a shadow mask. In an embodiment, the patterned conductive layer 123 includes a first layer of 500 angstrom thick titanium (Ti), a middle layer of 500 angstrom thick titanium-tungsten (TiW), and a 1  $\mu m$  to 2  $\mu m$  thick outer layer of gold (Au). In an embodiment, the patterned conductive layer 123 makes ohmic contact with the silicon interconnects 106.

[0056] A patterned conductive layer 122 may be formed on the passivation layer 133 within the via openings 120A and in electrical contact with the patterned conductive layer 123 as illustrated in FIGS. 31A-31B. Conductive layer 122 may be formed from the same or different material from conductive layer 123, and may have the same or different thicknesses. In an embodiment, conductive layer 123 has a thicker layer of gold. Conductive layers 122, 123 may form a continuous conductive layer along the via 120 side surfaces.

[0057] Referring now to FIGS. 32A-32B, a second dielectric layer may be blanket deposited over the top surface of the patterned SOI stack, while providing backside protection. As illustrated the second dielectric layer 126 is formed on the mesa structures 112, on dielectric layer 118 and in the vias 120. In an embodiment, the second dielectric layer 126 is formed within the via opening 120 adjacent the patterned silicon layer 140. In an embodiment, the second dielectric layer may have a higher dielectric constant or dielectric breakdown strength than dielectric layer 118, and has a thickness between 0.5  $\mu\text{m}$ - 10  $\mu m$ . For example, the second dielectric layer 126 a layer of Al<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub>, or HfO<sub>2</sub> deposited by atomic layer deposition (ALD). Following the formation of dielectric layer 126, the SOI substrate may then be diced, for example using laser dicing, to form a plurality of transfer heads.

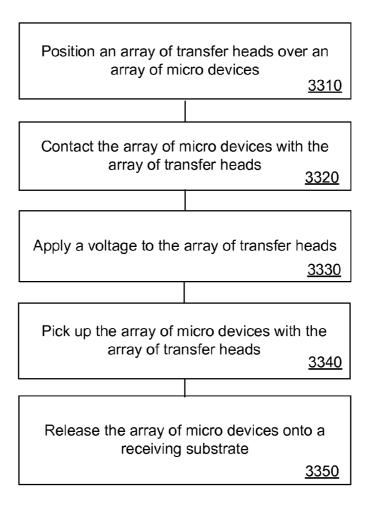

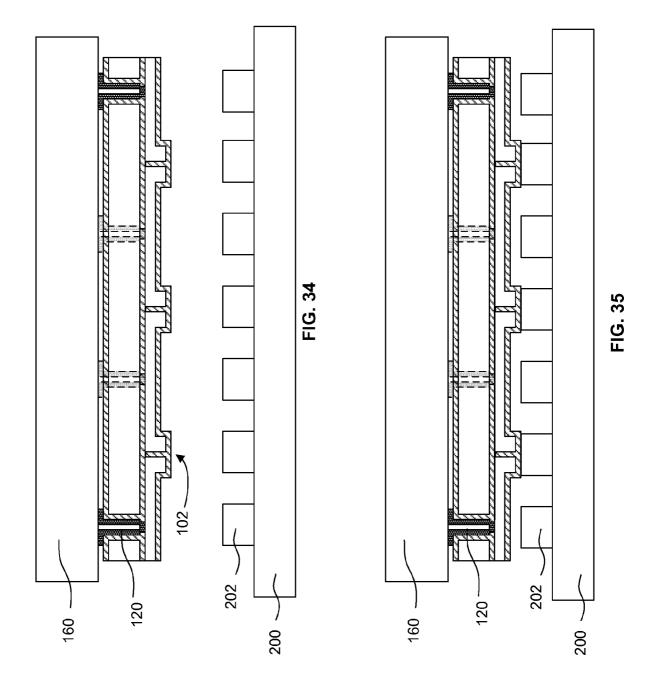

[0058] In accordance with embodiments of the invention, the dielectric layer 118 or 126 covering the mesa structures 112 has a suitable thickness and dielectric constant for achieving the required grip pressure for the micro device transfer head, and sufficient dielectric strength to not break down at the operating voltage. FIG. 33 is a flow chart illustrating a method of picking up and transferring an array of micro devices from a carrier substrate to a receiving substrate in accordance with an embodiment of the invention. At operation 3310 an array of transfer heads is positioned over an array of micro devices on a carrier substrate. FIG. 34 is a cross-sectional side view illustration of an array of micro device transfer heads 102 positioned over an array of micro devices on a carrier substrate 200 in accordance with an embodiment of the invention. At operation 3320 the array of micro devices are contacted with the array of transfer heads.

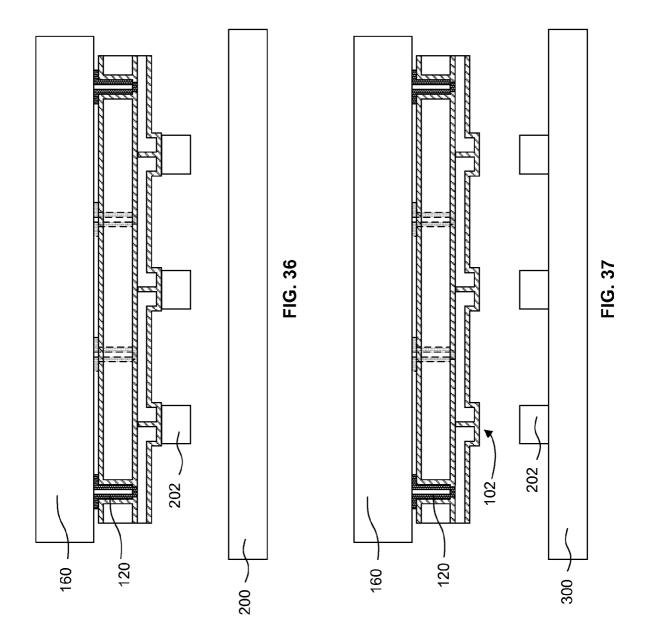

In an alternative embodiment, the array of transfer heads is positioned over the array of micro devices with a suitable air gap separating them which does not significantly affect the grip pressure, for example, 1 nm to 10 nm. FIG. 35 is a cross-sectional side view illustration of an array of micro device transfer heads 102 in contact with an array of micro devices 202 in accordance with an embodiment of the invention. As illustrated, the pitch of the array of transfer heads 202 is an integer multiple of the pitch of the array of micro devices 202. At operation 3330 a voltage is applied to the array of transfer heads 102. The voltage may be applied from the working circuitry within a transfer head assembly 160 in electrical connection with the array of transfer heads through vias 120. At operation 3340 the array of micro devices is picked up with the array of transfer heads. FIG. 36 is a cross-sectional side view illustration of an array of transfer heads 102 picking up an array of micro devices 202 in accordance with an embodiment of the invention. At operation 3350 the array of micro devices is then released onto a receiving substrate. For example, the receiving substrate may be, but is not limited to, a display substrate, a lighting substrate, a substrate with functional devices such as transistors or ICs, or a substrate with metal redistribution lines. FIG. 37 is a cross-sectional side view illustration of an array of micro devices 202 released onto a receiving substrate 300 in accordance with an embodiment of the invention.

[0059] While operations 3310-3350 have been illustrated sequentially in FIG. 33, it is to be appreciated that embodiments are not so limited and that additional operations may be performed and certain operations may be performed in a different sequence. For example, in one embodiment, an operation is performed to create a phase change in a bonding layer connecting the micro device to the carrier substrate prior to or while picking up the micro device. For example, the bonding layer may have a liquidus temperature less than 350 °C, or more specifically less than 200 °C. The bonding layer may be formed of a material which provides adhesion to the carrier substrate, yet also a medium from which the micro device is readily releasable. In an embodiment, the bonding layer is a material such as indium or an indium alloy. If a portion of the bonding layer is picked up with the micro device, additional operations can be performed to control the phase of the portion of the bonding layer during subsequent processing. For example, heat can be applied to the bonding layer from a heat source located within the transfer head assembly 160, carrier substrate 200, and/or receiving substrate 300.

**[0060]** Furthermore, operation 3330 of applying the voltage to create a grip pressure on the micro devices can be performed in various orders. For example, the voltage can be applied prior to contacting the array of micro devices with the array of transfer heads, while contacting the micro devices with the array of transfer heads, or after contacting the micro devices with the array of transfer heads. The voltage may also be applied prior to,

while, or after creating a phase change in the bonding layer.

[0061] Where the transfer heads 102 include bipolar silicon electrodes, an alternative voltage is applied across a the pair of silicon electrodes in each transfer head 102 so that at a particular point in the when a negative voltage is applied to one silicon electrode, a positive voltage is applied to the other silicon electrode in the pair, and vice versa to create the pickup pressure. Releasing the micro devices from the transfer heads 102 may be accomplished with a varied of methods including turning off the voltage sources, lower the voltage across the pair of silicon electrodes, changing a waveform of the AC voltage, and grounding the voltage sources.

[0062] In accordance with embodiments of the invention, manners of forming an array of transfer heads and manners for operating an array of transfer heads to transfer an array of micro devices have been described. Embodiments of the invention may be utilized to transfer a variety of micro devices such as, but not limited to, diodes, LEDs, transistors, ICs, and MEMS. In an embodiment, the array of transfer heads may be utilized to transfer an array of micro LED devices which are poised for pick up, such as the structures described in U.S. Patent Application No. 13/458,932.

[0063] In utilizing the various aspects of this invention, it would become apparent to one skilled in the art that combinations or variations of the above embodiments are possible for forming a micro device transfer head and head array, and for transferring a micro device and micro device array. Although the present invention has been described in language specific to structural features and/or methodological acts, it is to be understood that the invention defined in the appended claims is not necessarily limited to the specific features or acts described. The specific features and acts disclosed are instead to be understood as particularly graceful implementations of the claimed invention useful for illustrating the present invention.

#### Claims

40

50

45 **1.** A micro device transfer head array (100) comprising:

a base substrate (130);

a patterned silicon layer (140) over the base substrate, the patterned silicon layer including a silicon interconnect (104, 106) and an array of silicon electrodes (110) electrically connected with the silicon interconnect, wherein each silicon electrode includes a mesa structure (112) protruding above the silicon interconnect;

and

a dielectric layer (118) covering a top surface of each mesa structure;

15

25

30

35

40

45

50

55

wherein the array of silicon electrodes are integrated into a corresponding array of electrostatic transfer heads (102), each electrostatic transfer head configured to transfer a separate micro device.

- 2. The micro device transfer head array of claim 1, wherein each silicon electrode further comprises an electrode lead.

- 3. The micro device transfer head array of claim 1, further comprising a via (120) extending through the base substrate from a backside of the base substrate to the patterned silicon layer, and in electrical connection with the silicon interconnect and the array of silicon electrodes.

- **4.** The micro device transfer head array of claim 3, wherein the via terminates at a bottom surface of the patterned silicon layer.

- 5. The micro device transfer head array of claim 4, further comprising a passivation layer covering a side surface of the via within the base substrate, and a conductive layer on the passivation layer and in electrical contact with the bottom surface of the patterned silicon layer.

- **6.** The micro device transfer head array of claim 3, wherein the via extends through the patterned silicon layer.

- 7. The micro device transfer head array of claim 6, further comprising a passivation layer covering a side surface of the via within the base substrate, and a conductive layer on the passivation layer and in electrical contact with an interior side surface of the patterned silicon layer.

- **8.** The micro device transfer head array of claim 7, wherein a portion of conductive layer partially covers a top surface of the patterned silicon layer.

- 9. The micro device transfer head array of claim 3, further comprising an silicon oxide layer between the patterned silicon layer and the base substrate, and wherein the via extends through the silicon oxide layer.

- 10. The micro device transfer head array of claim 1, wherein the dielectric layer comprises a material selected from the group consisting of silicon oxide, hafnium oxide, aluminum oxide, and tantalum oxide.

- **11.** The micro device transfer head array of claim 3, further comprising:

a second via extending through the base substrate from the backside of the base substrate to the patterned silicon layer, and in electrical connection with a second silicon interconnect and a second array of silicon electrodes;

wherein each silicon electrode in the second array of silicon electrodes includes a mesa structure protruding above the second silicon interconnect, and the dielectric layer coves a top surface of each mesa structure.

- **12.** The micro device transfer head array of claim 11, wherein the array of silicon electrodes, and the second array of silicon electrodes are aligned to form an array of bipolar silicon electrodes.

- **13.** The micro device transfer head array of claim 11, wherein the via and the second via terminate at a bottom surface of the patterned silicon layer.

- **14.** The micro device transfer head array of claim 11, wherein the via and the second via extend through the patterned silicon layer.

- 15. The micro device transfer head array of claim 11, further comprising a first dielectric layer on the patterned silicon layer, wherein the first dielectric layer is removed from over the mesa structures; wherein the dielectric layer covering the top surface of the each mesa structure has a higher dielectric constant or dielectric breakdown strength than the first dielectric layer.

### Patentansprüche

Mikrovorrichtungsübertragungskopfanordnung (100), umfassend:

> ein Basissubstrat (130); eine musterförmig gelegte Siliziumschicht (140) über dem Basissubstrat, wobei die musterförmig gelegte Siliziumschicht eine Siliziumzwischenverbindung (104, 106) und eine Anordnung von Siliziumelektroden (110), die elektrisch mit der Siliziumzwischenverbindung verbunden ist, beinhaltet wobei jede Siliziumelektrode eine Mesa-Struktur (112), die über die Siliziumzwischenverbindung hervorragt, beinhaltet; und eine dielektrische Schicht (118), die eine obere Oberfläche jeder Mesa-Struktur bedeckt; wobei die Anordnung von Siliziumelektroden in eine entsprechende Anordnung elektrostatischer Übertragungsköpfe (102) integriert ist, wobei jeder elektrostatische Übertragungskopf eingerichtet ist, um eine getrennte Mikrovorrichtung zu übertragen.

20

25

35

40

45

50

55

- 2. Mikrovorrichtungsübertragungskopfanordnung nach Anspruch 1, wobei jede Siliziumelektrode weiter einen Elektronenleiter umfasst.

- 3. Mikrovorrichtungsübertragungskopfanordnung nach Anspruch 1, weiter umfassend eine vertikale Durchkontaktierung (120), die sich durch das Basissubstrat von einer Rückseite des Basissubstrats zu der musterförmig gelegten Siliziumschicht erstreckt und die sich in elektrischer Verbindung mit der Siliziumzwischenverbindung und der Anordnung von Siliziumelektroden befindet.

- **4.** Mikrovorrichtungsübertragungskopfanordnung nach Anspruch 3, wobei die vertikale Durchkontaktierung an einer unteren Oberfläche der musterförmig gelegten Siliziumschicht endet.

- 5. Mikrovorrichtungsübertragungskopfanordnung nach Anspruch 4, weiter umfassend eine passivierende Schicht, die eine Seitenoberfläche der vertikalen Durchkontaktierung innerhalb des Basissubstrats bedeckt, und eine leitende Schicht auf der Aktivierungsschicht, die sich in elektrischem Kontakt mit der unteren Oberfläche der musterförmig gelegten Siliziumschicht befindet.

- Mikrovorrichtungsübertragungskopfanordnung nach Anspruch 3, wobei sich die vertikale Durchkontaktierung durch die musterförmige gelegte Siliziumschicht erstreckt.

- 7. Mikrovorrichtungsübertragungskopfanordnung nach Anspruch 6, weiter umfassend eine passivierende Schicht, die eine Seitenoberfläche der vertikalen Durchkontaktierung innerhalb des Basissubstrats bedeckt, und eine leitende Schicht auf der passivierenden Schicht, die sich in elektrischem Kontakt mit einer inneren Seitenoberfläche der musterförmig gelegten Siliziumschicht befindet.

- 8. Mikrovorrichtungsübertragungskopfanordnung nach Anspruch 7, wobei ein Anteil der leitenden Schicht teilweise eine obere Oberfläche der musterförmig gelegten Siliziumschicht bedeckt.

- 9. Mikrovorrichtungsübertragungskopfanordnung nach Anspruch 3, weiter umfassend eine Siliziumoxidschicht zwischen der musterförmig gelegten Siliziumschicht und dem Basissubstrat, und wobei sich die vertikale Durchkontaktierung durch die Siliziumoxidschicht erstreckt.

- 10. Mikrovorrichtungsübertragungskopfanordnung nach Anspruch 1, wobei die dielektrische Schicht ein Material umfasst, das aus der Gruppe ausgewählt wird bestehend aus Siliziumoxid, Hafniumoxid, Aluminiumoxid und Tantalumoxid.

**11.** Mikrovorrichtungsübertragungskopfanordnung nach Anspruch 3, weiter umfassend:

eine zweite vertikale Durchkontaktierung, die sich durch das Basissubstrat von der Rückseite des Basissubstrats zu der musterförmig gelegten Siliziumschicht erstreckt und die sich in elektrischer Verbindung mit einer zweiten Siliziumzwischenverbindung und einer zweiten Anordnung von Siliziumelektroden befindet;

wobei jede Siliziumelektrode in der zweiten Anordnung von Siliziumelektroden eine Mesa-Struktur beinhaltet, die über die zweite Siliziumzwischenverbindung hervorragt und wobei die dielektrische Schicht eine obere Oberfläche jeder Mesa-Struktur bedeckt.

- 12. Mikrovorrichtungsübertragungskopfanordnung nach Anspruch 11, wobei die Anordnung von Siliziumelektroden und die zweite Anordnung von Siliziumelektroden ausgerichtet sind, um eine Anordnung von bipolaren Siliziumelektroden zu bilden.

- 13. Mikrovorrichtungsübertragungskopfanordnung nach Anspruch 11, wobei die vertikale Durchkontaktierung und die zweite vertikale Durchkontaktierung an einer unteren Oberfläche der musterförmig gelegten Siliziumschicht enden.

- 14. Mikrovorrichtungsübertragungskopfanordnung nach Anspruch 11, wobei die vertikale Durchkontaktierung und die zweite vertikale Durchkontaktierung sich durch die musterförmige gelegte Siliziumschicht erstrecken.

- 15. Mikrovorrichtungsübertragungskopfanordnung nach Anspruch 11, weiter umfassend eine erste dielektrische Schicht auf der musterförmig gelegten Siliziumschicht, wobei die erste dielektrische Schicht über den Mesa-Strukturen entfernt ist; wobei die dielektrische Schicht, die die obere Oberfläche jeder Mesa-Struktur bedeckt, eine höhere dielektrische Konstante oder dielektrische Durchschlagsfestigkeit aufweist als die erste dielektrische Schicht.

#### Revendications

Réseau de têtes de transfert de microdispositif (100) comprenant :

un substrat de base (130); une couche de silicium à motifs (140) sur le substrat de base, la couche de silicium à motifs comprenant une interconnexion en silicium (104, 106) et un réseau d'électrodes en silicium (110) reliées électriquement à l'interconnexion

20

25

30

en silicium.

dans lequel chaque électrode en silicium comprend une structure mesa (112) faisant saillie au-dessus de l'interconnexion en silicium ; et une couche diélectrique (118) recouvrant une surface supérieure de chaque structure mesa ; dans lequel le réseau d'électrodes en silicium est intégré à un réseau correspondant de têtes de transfert électrostatique (102),

chaque tête de transfert électrostatique étant configurée pour le transfert d'un microdispositif distinct.

- Réseau de têtes de transfert de microdispositif selon la revendication 1, dans lequel chaque électrode en silicium comprend en outre un conducteur d'électrode.

- 3. Réseau de têtes de transfert de microdispositif selon la revendication 1, comprenant en outre une traversée (120) s'étendant à travers le substrat de base depuis un côté arrière du substrat de base jusqu'à la couche de silicium à motifs, et en liaison électrique avec l'interconnexion en silicium et le réseau d'électrodes en silicium.

- 4. Réseau de têtes de transfert de microdispositif selon la revendication 3, dans lequel la traversée se termine au niveau d'une surface inférieure de la couche de silicium à motifs.

- 5. Réseau de têtes de transfert de microdispositif selon la revendication 4, comprenant en outre une couche de passivation recouvrant une surface latérale de la traversée à l'intérieur du substrat de base, et une couche conductrice sur la couche de passivation et en contact électrique avec la surface inférieure de la couche de silicium à motifs.

- **6.** Réseau de têtes de transfert de microdispositif selon la revendication 3, dans lequel la traversée s'étend à travers la couche de silicium à motifs.

- 7. Réseau de têtes de transfert de microdispositif selon la revendication 6, comprenant en outre une couche de passivation recouvrant une surface latérale de la traversée à l'intérieur du substrat de base, et une couche conductrice sur la couche de passivation et en contact électrique avec une surface latérale intérieure de la couche de silicium à motifs.

- 8. Réseau de têtes de transfert de microdispositif selon la revendication 7, dans lequel une portion de la couche conductrice recouvre partiellement une surface supérieure de la couche de silicium à motifs.

- 9. Réseau de têtes de transfert de microdispositif selon la revendication 3, comprenant en outre une couche

d'oxyde de silicium entre la couche de silicium à motifs et le substrat de base, et dans lequel la traversée s'étend à travers la couche d'oxyde de silicium.

- 5 10. Réseau de têtes de transfert de microdispositif selon la revendication 1, dans lequel la couche diélectrique comprend un matériau sélectionné dans le groupe se composant de l'oxyde de silicium, de l'oxyde d'hafnium, de l'oxyde d'aluminium et de l'oxyde de tantale.

- **11.** Réseau de têtes de transfert de microdispositif selon la revendication 3, comprenant en outre :

une deuxième traversée s'étendant à travers le substrat de base depuis le côté arrière du substrat de base jusqu'à la couche de silicium à motifs, et en liaison électrique avec une deuxième interconnexion en silicium et un deuxième réseau d'électrodes en silicium;

dans lequel chaque électrode en silicium dans le deuxième réseau d'électrodes en silicium comprend une structure mesa faisant saillie au-dessus de la deuxième interconnexion en silicium, et la couche diélectrique recouvre une surface supérieure de chaque structure mesa.

- 12. Réseau de têtes de transfert de microdispositif selon la revendication 11, dans lequel le réseau d'électrodes en silicium et le deuxième réseau d'électrodes en silicium sont alignés pour former un réseau d'électrodes bipolaires en silicium.

- 13. Réseau de têtes de transfert de microdispositif selon la revendication 11, dans lequel la traversée et la deuxième traversée se terminent au niveau d'une surface inférieure de la couche de silicium à motifs.

- 40 14. Réseau de têtes de transfert de microdispositif selon la revendication 11, dans lequel la traversée et la deuxième traversée s'étendent au travers de la couche de silicium à motifs.

- 45 15. Réseau de têtes de transfert de microdispositif selon la revendication 11, comprenant en outre une première couche diélectrique sur la couche de silicium à motifs, dans lequel la première couche diélectrique est retirée du dessus des structures mesa; dans lequel la couche diélectrique recouvrant la surface supérieure de chaque structure mesa présente une constante diélectrique ou une résistance à la rupture diélectrique supérieure à celle de la première couche diélectrique.

14

FIG. 33

# EP 2 834 840 B1

#### REFERENCES CITED IN THE DESCRIPTION

This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.

# Patent documents cited in the description

- WO 2011072372 A **[0005]**

- US 372222 A [0062]

• US 458932 A [0062]

| 专利名称(译)        | 带硅电极的微器件转移头                     |         |            |  |

|----------------|---------------------------------|---------|------------|--|

| 公开(公告)号        | EP2834840B1                     | 公开(公告)日 | 2016-12-28 |  |

| 申请号            | EP2013794179                    | 申请日     | 2013-05-16 |  |

| [标]申请(专利权)人(译) | 勒克斯维科技公司                        |         |            |  |

| 申请(专利权)人(译)    | LUXVUE科技股份有限公司                  |         |            |  |

| 当前申请(专利权)人(译)  | 苹果公司.                           |         |            |  |

| [标]发明人         | GOLDA DARIUSZ<br>BIBL ANDREAS   |         |            |  |

| 发明人            | GOLDA, DARIUSZ<br>BIBL, ANDREAS |         |            |  |

| IPC分类号         | H01L21/677 B81C1/00 B65G49/07   |         |            |  |

| 优先权            | 13/481592 2012-05-25 US         |         |            |  |

| 其他公开文献         | EP2834840A4<br>EP2834840A1      |         |            |  |

| 外部链接           | Espacenet                       |         |            |  |

# 摘要(译)

描述了微器件转移头阵列和由SOI衬底形成微器件转移阵列的方法。在一个实施例中,微器件转移头阵列包括基础衬底和在基础衬底上方的图案化的硅层。图案化的硅层可以包括硅互连件和与硅互连件电连接的硅电极的阵列。每个硅电极包括在硅互连上方突出的台面结构。介电层覆盖每个台面结构的顶面